About

I am an Associate Professor at Institute of Computing Technology, Chinese Academy of Sciences (ICT, CAS). I received my B.S. in Physics from Tsinghua University and my Ph.D. from ICT, CAS. My research focuses on automated chip design and code generation, with particular interest in systematically training chip design foundation models and building practical chip design systems powered by these models. I am also broadly interested in Embodied AI.

I am the lead contributor to the CodeV series, a family of fully open-source foundation models for HDL (e.g., Verilog) generation.

Feel free to reach me at huangdi[AT]ict.ac.cn.

News

4 papers were accepted to AAAI 2026 (2 oral) 🎉

2 papers were accepted to IEEE TCAD 🎉

We have open-sourced our HDL generation foundation models CodeV series on 🤗Hugging Face, along with their datasets🔥🔥🔥

4 papers were accepted to NeurIPS 2025 (1 spotlight) 🎉

Selected Publications

View All →

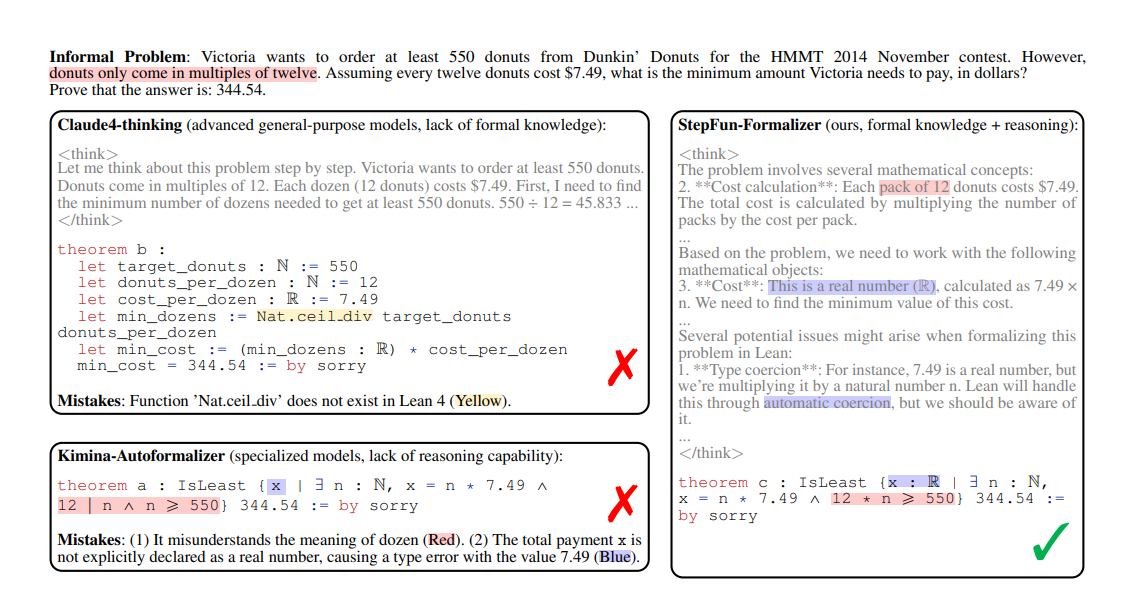

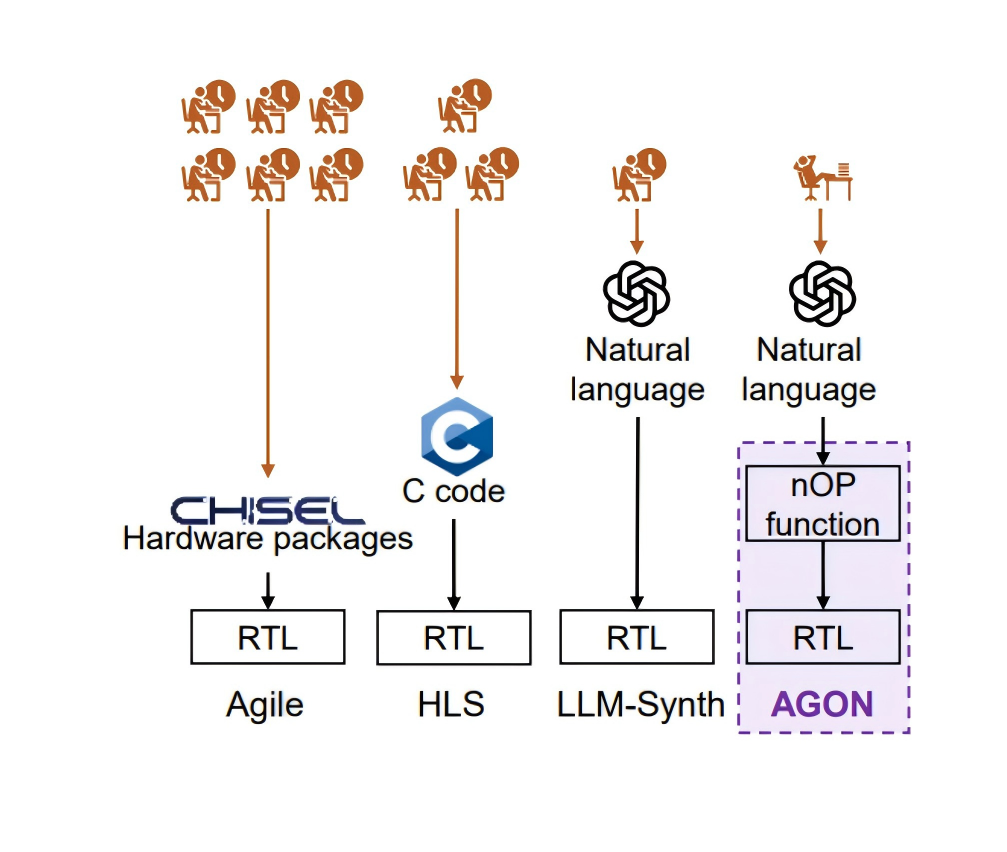

AGON: Automated Design Framework for Customizing Processors from ISA Documents

Chongxiao Li, Di Huang, Pengwei Jin, Tianyun Ma, Husheng Han, Shuyao Cheng, Yifan Hao, Yongwei Zhao, Guanglin Xu, Zidong Du, Rui Zhang, Xiaqing Li, Yuanbo Wen, Xing Hu, Qi Guo

IEEE TCAD 2025

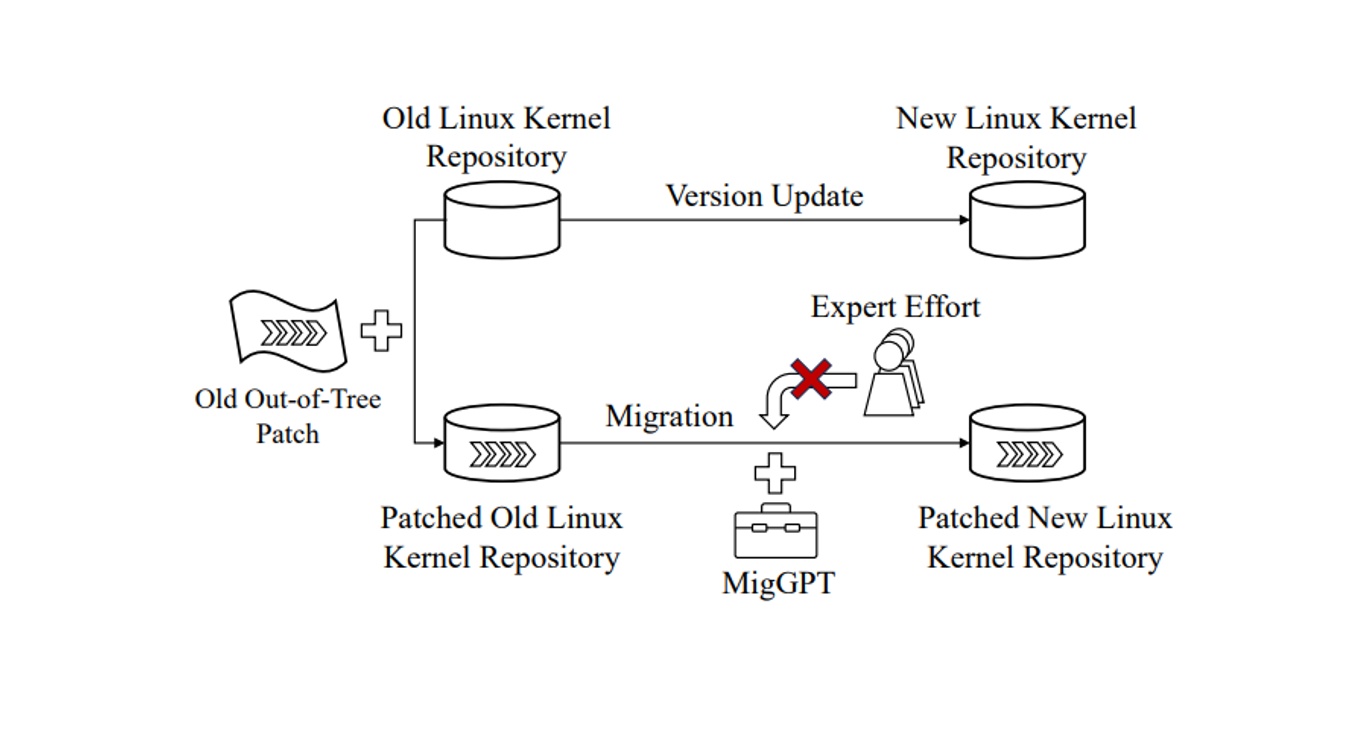

MigGPT: Harnessing Large Language Models for Automated Migration of Out-of-Tree Linux Kernel Patches Across Versions

Pucheng Dang, Di Huang, Dong Li, Kang Chen, Yuanbo Wen, Qi Guo, Xing Hu

NeurIPS 2025 Spotlight

CodeV: Empowering LLMs with HDL Generation through Multi-Level Summarization

Yang Zhao, Di Huang, Chongxiao Li, Pengwei Jin, Muxin Song, Yinan Xu, Ziyuan Nan, Mingju Gao, Tianyun Ma, Lei Qi, Yansong Pan, Zhenxing Zhang, Rui Zhang, Xishan Zhang, Zidong Du, Xing Hu

IEEE TCAD 2025

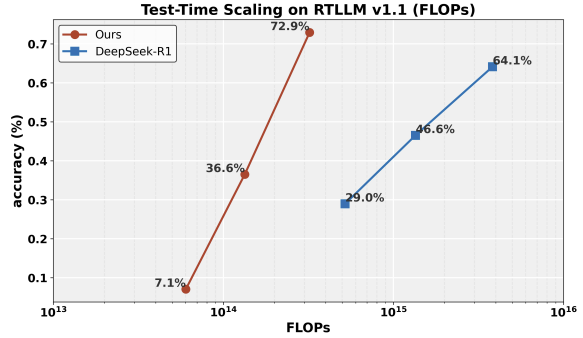

QiMeng-CodeV-R1: Reasoning-Enhanced Verilog Generation

Yaoyu Zhu, Di Huang, Hanqi Lyu, Xiaoyun Zhang, Chongxiao Li, Wenxuan Shi, Yutong Wu, Jianan Mu, Jinghua Wang, Pengwei Jin, Shuyao Cheng, Shengwen Liang, Xishan Zhang, Rui Zhang, Zidong Du, Qi Guo, Xing Hu, Yunji Chen

NeurIPS 2025

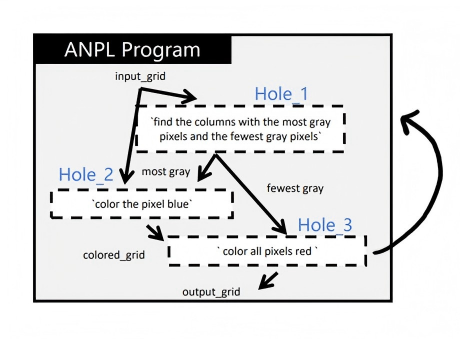

ANPL: Towards Natural Programming with Interactive Decomposition

Di Huang, Ziyuan Nan, Xing Hu, Pengwei Jin, Shaohui Peng, Yuanbo Wen, Rui Zhang, Zidong Du, Qi Guo, Yewen Pu, Yunji Chen

NeurIPS 2023

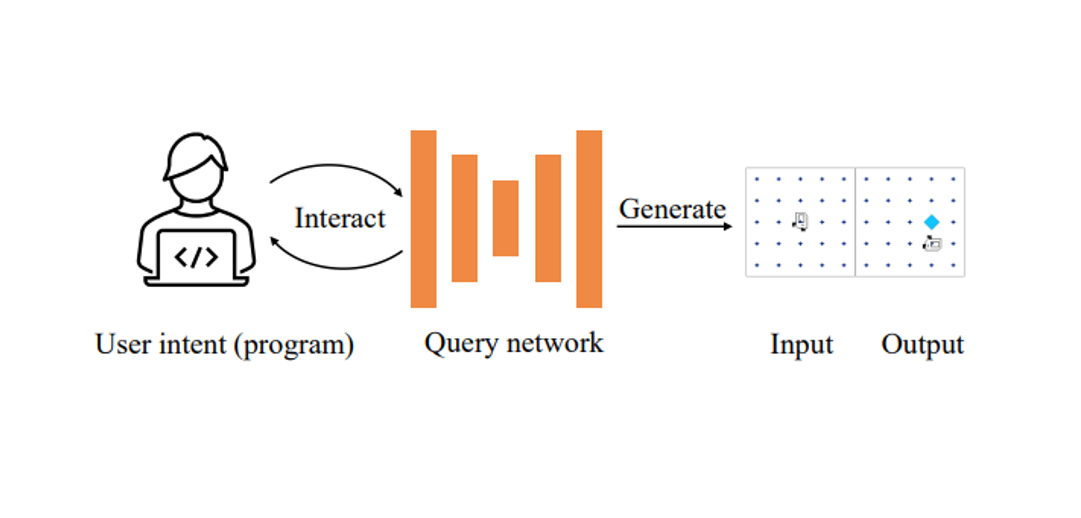

Neural Program Synthesis with Query

Di Huang, Rui Zhang, Xing Hu, Xishan Zhang, Pengwei Jin, Nan Li, Zidong Du, Qi Guo, Yunji Chen

ICLR 2022

Services

Neurips 2023-, ICLR 2024-, ICML 2024-, AAAI 2025-, AISTATS 2025

Invited Talks

LLM for Hardware Code Generation and Optimization @ CCF ADL

QiMeng: Automated Hardware and Software Design for Processor Chip @ AI4FACD Workshop @ ISCA 2025: